Leiterplatten | Herstellung | 2-lagig

Leiterplatten in der Herstellung

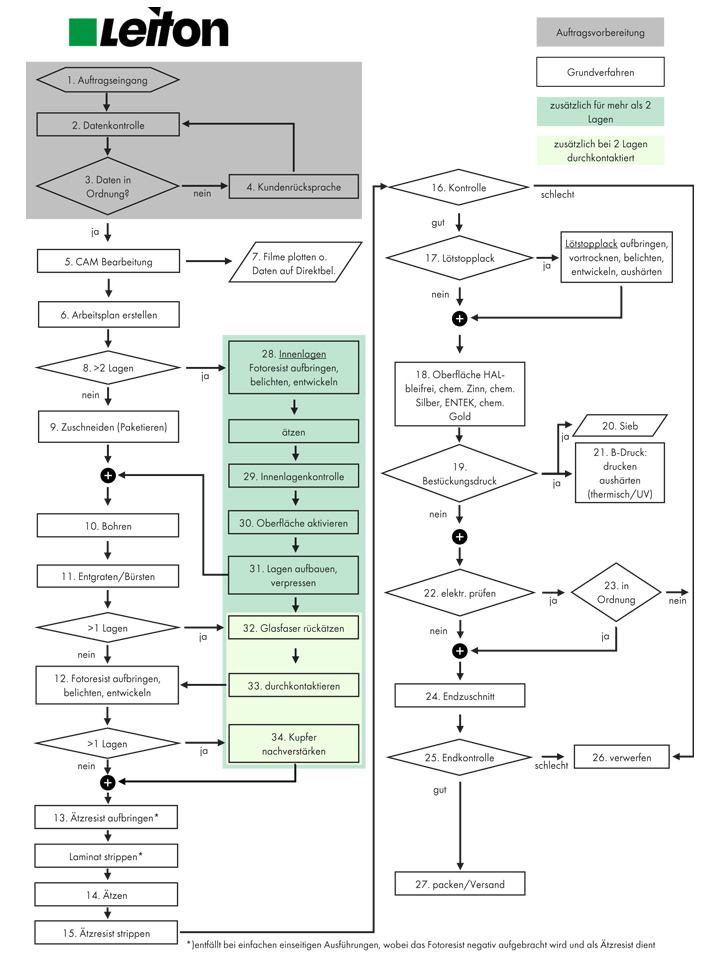

Die Leiterplattenherstellung erfolgt in einer Vielzahl von mechanischen, photosensitiven und chemischen Prozessen. Der Ablauf der Leiterplattenherstellung verläuft bei einer 2-lagigen Leiterplatte wie folgt:

Um einen Auftrag für die Leiterplattenfertigung entgegennehmen zu können, benötigt der Leiterplattenhersteller folgende Daten und Informationen:

- Gerberdaten oder andere Layoutdaten zur Umsetzung in Fertigungsdaten. Zum Beispiel Eagle, Target3001, TiCAD, Orcad, Sprint, Protel etc.

- Stückzahl

- Lieferzeit

- Leiterplattendicke (0,1 mm bis ca. 4,2 mm. Standard sind meist 1,6 mm)

- Leiterplattenmaterial (FR4, TG-Wert, CEM, Alu-IMS, Rogers, Isola oder andere Sondermaterialien)

- Kupferstärke (35µm bis 400µm Dickkupfer)

- Anzahl der Lagen, falls nicht eindeutig durch Gerber-Dateien definiert

- Einzelplatine oder Nutzentyp/-größe

- Mechanische Prozesse (Ritzen, Fräsen, Stanzen, Fasen usw.)

- Oberflächenveredelung: HAL, chemisch Zinn (Sn), chemisch Gold (NiAu)/ENIG, chemisch Nickel-Palladium-Gold (ENEPIG), chemisch Silber (Ag), Fingergold/Hartgold, OSP usw.

- Lötstopplack (gewünschte Farbe, Standardfarbe ist grün)

- Bestückungsdruck, falls erforderlich (gewünschte Farbe, Standardfarbe ist weiß)

- Elektrischer Test (E-Test) oder andere Tests, z. B. Widerstandsmessungen, Impedanzkontrolle

Die Datenkontrolle wird gemeinhin auch als DRC (Design Rules Check) bezeichnet. Hierbei werden die Daten zunächst auf Vollständigkeit und dann auf die fertigungsrelevanten Regeln der Leiterplattenherstellung hin überprüft. Dazu zählen vor allem:

- Pads mittig zum Bohrprogramm "snappen".

- Ausreichende Restringgröße der Kupferpads um die Bohrungen überprüfen.

- Kleinste Bohrdurchmesser gemäß Technologieaufwand überprüfen.

- Leiterbahndicken und -Abstände überprüfen. Vorgaben je nach Feinheit der Technologie. Meist ist die 6mil-Technologie (ca. 0,15mm) heutzutage Standard, teilweise wird aber 4mil oder feiner benötigt.

- Leiterbahnen mit Ätzzugaben versehen, um der fertigungsbedingten Verjüngung entgegenzuwirken.

- Trennung der durchkontaktierten- und nicht durchkontaktierten Bohrungen in verschiedene Bohrprogramme.

- Rückstellung der Kupferflächen von der Fräskontur der Leiterplatte.

- Allgemeine Plausibilitätsprüfung (Leiterbahnkreuzungen, fehlende Bohrungen, Freistellungen etc.)

- Lötstoppmasken größer als die Pads anschwellen und zu dünne Stege schließen.

- Fräskontur auf Lücken hin überprüfen, Haltestege setzen und verschiedene Fräsdurchmesser zuordnen.

- Fräs- und Bohrwege optimieren, um Zeit bei der Herstellung der Leiterplatten einzusparen.

Die Daten der Leiterplatten werden entsprechend der gewünschten Technologien hin auf Schlüssigkeit und Machbarkeit hin überprüft. Je nach Fertigungsverfahren gibt es verschiedene Grenzen in der Fertigung der Leiterplatte. Sind diese Grenzen überschritten und kann eine Anpassung in der CAM-Bearbeitung nicht erfolgen, muss der Kunde informiert werden. Nicht möglich sind jedoch Funktionsprüfungen der Schaltung. Die Daten gelten für den Leiterplattenhersteller als in Ordnung, wenn alle Design Rules eingehalten werden und die Platine so gefertigt werden kann. Fehler im Layout können nicht überprüft werden, da dem Hersteller oft nicht einmal die genaue Verwendung oder die später verwendeten Bauteile bekannt sind.

Bei Unklarheiten bezüglich der Fertigungsdaten wird der Kunde informiert. Die Benachrichtigung erfolgt per Email oder telefonisch, je nach Dringlichkeit. Die Email hat den Vorteil, Screenshots der fraglichen Stellen in der Leiterplatte mit zu senden, die bestimmte Probleme aufzeigen.

n der CAM Bearbeitung werden die aufbereiteten und produktionsfertigen Daten mit Maschinendaten verknüpft. Filmdaten werden mit Passmarken und bestimmten Rahmen versehen. Bohr- und Fräsdaten werden mit Passbohrungen verknüpft und in die Maschinenformate Sieb & Meyer oder Excellon umgewandelt. Gängige Programme zur CAM Bearbeitung von Leiterplatten sind:

- CAM350 (https://www.cadcompact.de/index2.htm)

- Genesys 2000

- UCAM (www.mania.de)

- CAMMaster, ehemals Lavenir (https://www.pentalogix.com)

Der Arbeitsplan enthält alle für die Herstellung der Leiterplatten erforderlichen Informationen bezüglich der Arbeitsschritte, Materialien, Stückzahlen und Terminvorgaben. Einem sorgfältig erstellten vollständigen und detaillierten Arbeitsplan kommt insbesondere dann eine große Bedeutung zu, wenn spezielle Materialien und Stoffe, sowie vom Standard abweichende Fertigungsschritte für die Leiterplattenherstellung erforderlich sind. Da in dieser Phase die Weichen für eine erfolgreiche und den Kundenwünschen entsprechende Produktion gestellt wird, kommt der Arbeitsplanerstellung eine besondere Verantwortung zu Teil, die nur durch Sorgfalt und langjährige Erfahrung in der Leiterplattenherstellung zu tragen ist.

Für die Leiterplattenherstellung benötigt man Filme. Diese Filme werden für spätere Belichtung von Kupferstrukturen und Lötstoppmasken, sowie anderen Druckbildern wie Bestückungsdruck oder Viafüllerdruck erstellt. Auch Kontrollfilme, die Bohrlöcher und Fräskonturen anzeigen, werden geplottet. Für die Filmerstellung werden heutzutage Laserplotter mit der Möglichkeit zur Abbildung von hoch auflösenden Strukturen und Leiterbildern verwendet. Nach dem plotten der Filme in Dunkelkammern werden diese entwickelt. Verwendet werden so genannte Silberfilme oder Diazofilme. Letztere sind widerstandsfähiger und werden insbesondere in der Serienfertigung von Leiterplatten verwendet, da sie häufiger verwendet werden können.

Anbieter von Plottern für Leiterplattenfilme:

Mania Technologie AG - www.mania.de

Platinen mit mehr als zwei Lagen werden als Multilayer bezeichnet. Diese Leiterplatten durchlaufen zunächst einen separaten Prozess, um die Innenlagen herzustellen, bevor die Leiterplatten schließlich wieder dem gleichen Prozess folgen, wie es für 2-lagige Platinen üblich ist.

Die Basismaterialien (Isolierträger mit 1 oder 2-seitiger Kupferbeschichtung) werden zumeist in großen Formaten angeliefert und erst beim Leiterplattenhersteller auf das eigentliche Fertigungsformat zugeschnitten. Hierfür verwendet man je nach Materialart entweder Schlagscheren oder bei empfindlichen Materialien wie Keramik für Hochfrequenzanwendungen Fräsmaschinen. Wenn die Technologie es erlaubt, werden um Zeit zu sparen Leiterplattenzuschnitte in so genannte Pakete übereinander gelegt und verstiftet. Unterhalb dieses Paketes benutzt man 1,5mm bis 2mm dicke Presspappe und oberhalb Aluminiumlagen. Die Presspappe ermöglicht eine Durchbohrung des gesamten Pakets, ohne in den Bohrtisch zu treffen. Sie wird nur als Abstandshalter verwendet. Die circa 0,15mm dicke Aluminiumplatte oberhalb sorgt für eine "Schmierung" des Bohrers und eine einwandfreie Führung.

Durch diese Paketierung der Leiterplatten kann man mit einem Bohrvorgang mehrere Zuschnitte gleichzeitig bohren. Hierzu werden die Stapel an zwei Seiten gebohrt und mit Stiften zu einem Paket fixiert. Die Einschränkungen entstehen hier bei sehr kleinen Bohrdurchmessern, wodurch die Paketstärke reduziert werden muss. Eine Paketdicke darf je nach Bohrlochdurchmesser eine bestimmte Dicke nicht überschreiten, wodurch auf die Materialstärke selbst auch zum Kostenbeeinflussenden Faktor werden kann.

Das Bohren der Leiterplatten erfolgt in Paketen. Das Paket wird auf der Bohrmaschine in die Aufnahmen (Stifte des Paketes) aufgelegt (von Hand oder mit einem automatischen Beladers). Die Maschine bohrt dann mittels des eingelesenen Bohrprogramms die Löcher und wechselt entsprechend der Durchmesser automatisch die Bohrer. Die Geschwindigkeit des Bohrens hängt von den verwendeten Bohrdurchmessern ab. Kleine Bohrdurchmesser drehen zwar schneller müssen aber mit einem langsameren Hub gebohrt werden. Zudem ist die Dicke der Leiterplattenpakete begrenzt. Je nach Bohrdurchmesser sind die Eintauchgeschwindigkeit und die Drehzahl unterschiedlich.

Informationen und Anbieter von Bohrmaschinen für die Leiterplattenfertigung:

Schmoll Maschinen GmbH - www.schmoll-maschinen.de

Bohren von Multilayern

Da beim Bohrvorgang von Multilayern das Verpressen der Innenlagen bereits vorausgegangen ist, müssen die Bohrungen exakt auf die Innenlagen passen. Dies wird dadurch erschwert, dass eine vollflächige Kupferschicht der Außenlagen die Sicht auf die Innenlagenstrukturen verhindert. Hierzu werden an festgelegten Positionen im Aussenrahmen befindliche Passermarken freigelegt und dann Aufnahmebohrungen für die Maschine eingebracht. Die neusten Bohrmaschinen verfügen über Röntgensysteme. Somit werden die Innenlagen sichtbar und das Bohrprogramm kann noch genau auf die innen liegenden Strukturen ausgerichtet werden.

Bohren von Sacklöchern (blind vias)

Für bestimmte Anwendungen bei Multilayern sind Löcher möglich, die nicht die gesamte Leiterplatte durchbohren. So können Innenlagen an nur eine bestimmte Außenlage angebunden werden. Dieses Z-Achse-Bohren wird auch als Sacklochbohren oder "blind vias" bezeichnet. Hierbei sind jedoch keine Paketierungen möglich. Des Weiteren ist das Aspektverhältnis zwischen Bohrdurchmesser und Lochtiefe zu beachten. Ein Aspektverhältnis von 1:1 gilt als unkritisch, um später eine Kontaktierung der Innenlage zu ermöglichen. Sind die Löcher viel tiefer als breit kann das Loch später im Durchkontaktierungsprozess der Leiterplatte nur schwierig durchflutet werden.

Bohren von vergrabenen Löchern (burried vias)

Das Bohren von vergrabenen Löchern ist lediglich eine Prozessabweichung vom normalen Herstellungsprozess von Multilayer- Leiterplatten. Bevor die Innenlagen verpresst werden, werden diese einzeln gebohrt, durchkontaktiert und gepluggt (verschlossen). Es können natürlich auch mehrere Innenlagen miteinander verbunden werden. Hierzu ist ein weiterer Pressvorgang erforderlich. Nach dem endgültigen Verpressen sind diese Durchkontaktierungen von Außen nicht sichtbar, daher "vergraben". Für den Bohrprozess selber stellt dies keine besonderen Herausforderungen dar. Der Aufwand zur Leiterplattenherstellung steigt jedoch an.

Nach dem Bohrdurchgang muss an den Leiterplatten der entstandene Bohrgrat entfernt werden. Hierfür werden nach dem entstiften der Leiterplattenstapel meist Bürstmaschinen mit Schleifwalzen verwendet. Neben dem Entgraten wird die Kupferoberfläche dabei gesäubert und angeraut, was eine optimale Kupferoberfläche für die Haftung des Fotoresist schafft.

Informationen und Anbieter für Bohrlochreinigung von Leiterplatten: Höllmüller Maschinenbau GmbH - https://www.hms-germany.de/

Um das Leiterbild der späteren Leiterplatte aufbringen zu können, wird auf die Platine entweder mittels eines Laminators UV-lichtempfindlicher Folie aufgebracht oder es wird mit einem Vorhanggießer eine hauchdünne UV-lichtempfindliche Lackschicht gegossen und getrocknet. Dann wird der geplottete Film in einem Belichter von Hand oder automatisch passend zum Bohrbild ausgerichtet und belichtet. Es gibt auch so genannte Direktbelichter. Hier wird das Leiterbild ohne Film direkt mittels Laserstrahl auf die fotosensible Schicht aufgebracht. Die belichteten Stellen härten aus, so dass bei der anschließenden Entwicklung bei allen nicht belichteten Flächen das Kupfer freigelegt wird.

Auf die zuvor freigelegten Kupferflächen wird mittels Strom Zinn oder ein ähnliches ätzresistentes Material aufgebracht welches beim Ätzvorgang die Kupferflächen schützt. Der Fotoresist wird dann mit alkalischer Lösung entfernt. Jetzt liegen die wegzuätzenden Flächen als Kupfer frei.

Das Kupfer wird mit einer alkalischen oder sauren Lösung abgeätzt. Hierfür wird in der industriellen Leiterplattenfertigung überwiegend mit einer Ammoniumchloridhaltigen Kupferchloridlösung gearbeitet. Durch das Einätzen von Kupfer steigt die Kupferkonzentration und damit die Dichte der Lösung. Um die Kupferionen bei pH-Werten um 8,5 in Lösung zu halten, bindet man sie mit Ammoniak im Kupfertetraminkomplex.

Informationen und Anbieter für Leiterplattenätztechnik:

- Atotech Deutschland GmbH - www.atotech.com

- MacDermid Enthone - https://www.macdermidenthone.com/

- Höllmüller Maschinenbau GmbH - https://www.hms-germany.de/

Das Zinn wird mit einer meist salz- und salpetersauren Lösung entfernt. Wenn Fotoresist als Ätzresist verwendet wurde wird dieser mit einer alkalischen Lösung gestrippt Nach diesem Ätzvorgang sind die Leiterplatten zum ersten mal technisch funktionsfähig.

Informationen und Anbieter für Leiterplattenätztechnik:

- Höllmüller Maschinenbau GmbH - https://www.hms-germany.de/

Die optische Kontrolle kann visuell mit Leuchtlupe oder automatisch erfolgen. Hierfür verwendet man so genannte AOI-Systeme (Automatic Optical Inspection). Die Leiterplattenoberfläche wird mittels einer Kamera aufgenommen und mit den zuvor aus den Layoutdaten erzeugten Daten verglichen. Fehlstellen zeigt der Computer an, so dass die Innenlagen entweder verworfen oder repariert werden können.

Informationen und Hersteller von AOI Systemen für die Prüfung von Leiterplatten:

- Orbotech Ltd. - www.orbotech.com

Der Lötstopplack hat die Funktion Zinn nur dort aufzubringen wo es benötigt wird. Das verhindert bei späteren Lötprozessen auch das Entstehen von Zinnbrücken. Wie der Name schon sagt, wird auf diesen Flächen "das Lot gestoppt" und findet keine Haftung auf der Leiterplatte. Nebenbei verleiht er der Platine ihre typische grüne Farbe. Heutzutage sind jedoch alle anderen Farben herstellbar. Wenn gewünscht, wird Lötstopplack auf den Leiterplatten aufgebracht. Im Allgemeinen geschieht das im Vorhanggieß- oder im Siebdruckverfahren. Dann wird der Lack vorgetrocknet und wie schon vorher beim Leiterbild belichtet und entwickelt. Anschließend wird der Lack thermisch ausgehärtet. In besonderen Fällen wird eine Folie auflaminiert (wie beim Fotoresist) Der Vorteil hier ist, das Löcher bis zu einem Durchmesser von ca. 3mm geschlossen werden können, was bei der Prüfung einer bestückten Leiterplatte mittels eines Vakuumadapters nötig ist.

Anbieter und Informationen über Lötstopplack für Leiterplatten:

Peters GmbH & Co. KG - www.peters.de

Die Oberflächen für die Leiterplatten unterscheiden sich in der Herstellung vor allem bezüglich der Abscheidung.

HAL

HAL (Hot Air Levelling) bringt eine Zinnoberfläche auf, indem die Leiterplatten nach einer Oberflächenaktivierung (fluxen) in ein heißes Zinnbad getaucht werden. Auf den lötstoppfreien Metalloberflächen setzt sich so das Zinn fest. Beim Herausziehen wird mit hohem Druck das in den Löchern vorhandene Zinn heraus geblasen. Vorteilhaft ist dieses Verfahren vor allem wegen des schnellen Beschichtungsprozesses, sowie der meist dicken Zinnbeschichtung und damit bessere Verwendbarkeit für spätere Mehrfachlötvorgänge und längere Lagerung. Nachteile entstehen durch die hohe thermische Belastung der Leiterplatte und der Schwierigkeit, sehr feine Pads planar zu beschichten. Platinen mit Fine-Pitch Bauteilen sollten daher mit einer Oberfläche gefertigt werden, die gleichmäßiger auf den Pads liegt.

Chemisch Zinn

Das chemische Zinn wird in Abscheidungsbädern aufgebracht. Dieser Prozess dauert etwas länger, bildet aber planare Oberflächen heraus, die sich bestens zur Bestückung von Fine-Pitch Bauteilen eignen. Der Nachteil des chemischen Zinns liegt zum einen in der begrenzten Verwendbarkeit für Mehrfachlötvorgänge, sowie in einer eingeschränkten Lagerfähigkeit. Es empfiehlt sich stets, Leiterplatten mit chemisch Zinn umgehend zu verarbeiten.

Chemisch Silber

Wie chemisch Zinn handelt es sich hierbei um eine Oberfläche die langsam und gleichmäßig durch Abscheidung aufgetragen wird. Erfahrungsgemäß ist diese Oberfläche jedoch noch empfindlicher als chemisch Zinn. Unsachgemäße Handhabung (Verschmutzung, Fingerabdrücke etc.) können hier sehr schnell zu mangelnder Lötbarkeit führen.

OSP

OSP (Organic Solderable Preservative) wird durch tauchen oder im Durchlaufverfahren aufgetragen und schützt die Kupferfläche primär vor Oxidation. Zum späteren löten muss hier mehr Zinn hinzugefügt werden, um eine Verbindung zwischen Bauteil und Leiterplatte herzustellen. Dieses Verfahren ist insbesondere in der billigen Massenfertigung verwendbar, da hier über die Menge gesehen Rohstoffkosten durch das entfallende Zinn eingespart werden können. Der Ruf dieser Oberfläche ist durch frühe (gescheiterte) Versuche ähnlicher Verfahren jedoch stark in Mitleidenschaft gezogen worden, weswegen es in Deutschland und Westeuropa so gut wie gar nicht nachgefragt und angeboten wird.

Chemisch Nickel-Gold

Chemisch Nickel-Gold ist die für nahezu alle Verfahren beste Oberfläche. Sowohl bei Fine-Pitch, Mehrfachlötvorgängen, Langzeitlagerung als auch bei Leiterplatten die Bonding benötigen ist chemisch Nickel-Gold eine sehr gute Oberfläche. Demgegenüber stehen jedoch sehr hohe Fertigungskosten. Diese hohen Kosten entstehen nicht alleine durch den Rohstoff Gold (die dickere Nickelschicht kann sogar teurer sein), sondern insbesondere durch die sehr komplizierte und empfindliche Badführung.

Informationen und Anbieter für Leiterplattenoberflächentechnik:

Atotech Deutschland GmbH - www.atotech.com

MacDermid Enthone - https://www.macdermidenthone.com/

Bestückungsdruck wird auch als Kennzeichnungsdruck bezeichnet und stellt eine elektrisch unbedeutende Schrift auf der Leiterplatte dar, die zur späteren Orientierung bei der Bestückung oder bei der Benutzung der Platine hilfreich ist. Standardfarben sind weiß oder gelb, da diese besonders gut auf dem grünen Lötstopplack der Leiterplatten sichtbar sind. Zu beachten ist hier, dass die Strukturen des Bestückungsdrucks auf Grund der Maschen im Sieb begrenzt sind. Beschriftungen von 0,2mm sind noch gut lesbar. Für dünnere Strukturen müssen feinere Siebe verwendet werden.

Informationen und Anbieter für Leiterplattenbestückungsdruck:

Peters GmbH & Co. KG - www.peters.de

Der Bestückungsdruck wird mit Hilfe eines Siebs erzeugt. Das ist ein in einen Rahmen gespanntes Netzgewebe. Zur Herstellung der Vorlage wird auch hier eine lichtempfindliche Emulsion aufgetragen, auf der das Druckbild mittels Film abgelichtet wird. Auch hier härtet der belichtete Teil aus, und der Rest wird mit Wasser aus dem Gewebe gewaschen. Alles was gedruckt werden soll wird hier nicht belichtet, sodass die Farbe hier mit einer Rakel durchgedrückt und auf der Leiterplatte abgebildet wird.

Das kann per Hand oder auch in vollautomatischen Maschinen geschehen. Das Sieb wird auf einem Siebdrucktisch passend zu der Leiterplatte ausgerichtet. Dann wird mit einer Rakel die Farbe mit gleichmässigem Druck durch die offenen Siebmaschen gepresst.

Seit kurzem gibt es auch Druckautomaten, die ähnlich wie ein Tintenstrahldrucker funktionieren. Der Vorteil hier liegt darin, dass kein Sieb vonnöten ist und der Druck direkt aus den CAD Daten generiert wird. Das Verfahren ist besonders interessant für Kleinststückzahlen und Prototypen Leiterplattenhersteller. Je nach Lackart wird dieser dann thermisch oder mit UV Licht auf der Leiterplatte ausgehärtet. Meist erfolgt dies in einem Durchlaufofen, durch den die Leiterplatten langsam auf einem Fließband befördert werden.

Das elektrische Prüfen der Leiterplatte kann mit einem Nadelbetttester (auch Adaptertester) oder einem Fingertester (auch Flying Probe) geschehen. Überprüft wird hier, ob die Leiterplatte so genannte Opens oder Shorts hat (Kurzschlüsse oder offene Verbindungen). Dafür werden anhand der Layoutdaten Netzlisten am Computer erstellt. Anhand dieser Netzlisten prüfen die Geräte jeweils, ob alle Verbindungen innerhalb des jeweiligen Netzes in Ordnung sind (Prüfung auf offene Verbindungen), sowie ob Verbindungen zu anderen Netzen vorliegen (Prüfung auf Kurzschlüsse).

Beim Adaptertester wird eine Adapterplatte gebohrt, die an allen Prüfstellen mit Kontaktnadeln bestückt wird. Die Prüfung erfolgt hier sehr schnell und ist für größere Stückzahlen geeignet. Der hohe Aufwand für den Adapterbau sorgt hier meist für sehr hohe Setup Kosten. Der Fingertester hat 4 bis 8 spitze Prüffinger je Seite, welche die Leiterplattenkontakte nach den im CAD Programm erstellten Netzlisten abtastet. Hier liegt der Vorteil darin, dass auch Einzelstücke kostengünstig geprüft werden können, da der aufwendige Adapterbau entfällt. Allerdings können bei sehr komplexen Leiterplatten Prüfzeiten von 30 Minuten und mehr entstehen.

Anbieter von elektrischen Testern für Leiterplatten:

Mania Technologie AG - www.mania.de

Das Testprogramm zeigt an, ob die Leiterplatte erfolgreich geprüft wurde. Die meisten heute gängigen Testprogramme zeigen zudem die Fehlerstelle auf dem Monitor an. So können gegebenenfalls bei Kurzschlüssen letzte Maßnahmen zu einer Korrektur vorgenommen werden, indem diese ungewollte Verbindung herausgekratzt wird. Ob dies möglich und sinnvoll ist, hängt von der Feinheit der Strukturen auf der Leiterplatte, sowie wirtschaftlichen Faktoren ab.

Der Endzuschnitt der Leiterplatten erfolgt je nach Kundenwunsch auf verschiedenen Maschinen. Gängig ist das Fräsen, bei dem zunächst alle nicht durchkontaktierten Bohrungen gesetzt werden. Anschließend fräst ein Fräser die Platinen gemäß der Kontur aus. Optimal sind hier Fräser von 2,0 oder 2,4mm zu verwenden. Diese können schneller fräsen und erlauben auf Grund ihrer Stabilität eine Paketierung. Daher sind dünnere Fräser im Aufwand und der Kostenkalkulation ein stark Einfluss nehmender Faktor.

Ein anderes gängiges Verfahren ist das Ritzen. Diese bietet sich bei kleinen Platinen an, da zwischen den Leiterplatten keine Abstände benötigt werden und die Fläche optimal ausgenutzt werden. Kann. Beim Ritzen wird die Leiterplatte mit 2 Ritzscheiben beidseitig mit einer 30° V-Nut ca. je 1/3 Leiterplattendicke eingekerbt. Nachteile liegen hier in der unsauberen Kontur und höherer Toleranzen, sowie dass nur Geraden geritzt werden können. Neuere Sprungritzmaschinen erlauben es aber, dass bestimmte Stellen nicht durchritzt werden. Immer häufiger werden Kombinationen aus ritzen und Fräsen. Schwierige Konturen werden hier mit dem Fräser bearbeitet, während gerade Strecken geritzt werden. Insbesondere in der Großserienfertigung von Leiterplatten wo mehrere Platinen in einem Nutzen liegen, ist dies üblich.

Ein ausschließlich in der Massenfertigung verwendetes Verfahren ist das Stanzen. Der Vorteil liegt in einer enorm hohen Geschwindigkeit der Vereinzelung der Leiterplatten. Nachteilig sind hier zunächst die einmalig anfallenden Kosten für das Stanzwerkzeug, sowie eine unsaubere Kontur und größere Toleranzen der Leiterplattenkontur.

Anbieter von Ritz- und Fräsmaschinen für die Leiterplattenfertigung:

- LHMT GmbH - www.lhmt.de

- HML Multilayer GmbH - www.hml-hr.com

- Schmoll Maschinen GmbH - www.schmoll-maschinen.de

In diesem letzten Schritt vor dem Versand werden die Leiterplatten erneut auf Auffälligkeiten und offensichtliche Fehler hin überprüft. Kratzer, Konturabweichungen und Fehler im Lötstopplack oder der Oberflächen stehen hier im Fokus der Leiterplattenendkontrolle.

Leiterplatten, die eine Prüfung nicht erfolgreich bestanden haben werden in eigens dafür bereitgestellten Containern gesammelt und einem Recyclingprozess zugeführt. Die noch auf den Leiterplatten enthaltenen Rohstoffe wie Zinn und Kupfer werden abgelöst und wieder verwertet. Das Epoxydharz wird zermahlen und ebenfalls für die Kunststoffherstellung wieder aufbereitet. Geregelt werden die erlaubten Stoffe in Leiterplatten, sowie der Umgang mit Leiterplattenschrott in der RoHS/WEEE Richtlinie.

Weitere Informationen zu RoHS/WEEE der europäischen Kommission:

https://ec.europa.eu/consumers/odr/main/index.cfm?event=main.adr.show

Die Verpackung von Leiterplatten erfolgt meist durch Luftdichtes einschweißen in Plastikfolien. Teilweise kann Seidenpapier als Kratzschutz zwischen den Leiterplatten verwendet werden oder eingeschweißte Salzbeutel sollen den Leiterplatten den Rest an Feuchtigkeit entziehen. Der Versand erfolgt innerhalb Deutschland und Europa meist per Kurier (Post, DHL, UPS, FedEx etc.). Für eilige Lieferungen können Direktboten bestellt werden. Großserien aus Asien bieten generell drei verschiedene Versandarten als Möglichkeit: Seefracht (ca. 3 Wochen), See-Luftfracht (ca. 2 Wochen) oder Luftfracht (ca. 3 Tage).

Links zu Frachtunternehmen:

- UPS - www.ups.com

- FedEX - www.fedex.com

- DHL - www.dhl.de

- Hartrodt Group - www.hartrodt.de

Die Innenlagen werden in Multilayern (Mehrlagenschaltungen), wie es der Name schon sagt, innerhalb der Leiterplatten verwendet. Innenlagen sind später von außen nur noch schwer im Multilayer erkennbar.

Die Kontrolle der Innenlagen kann auf verschiedene Weisen erfolgen. Bei sehr feinen Leiterbahnstrukturen bietet sich eine erste elektrische Prüfung an. Ist dies aus Kostengründen nicht erwünscht oder nötig, findet eine optische Kontrolle der Innenlagen statt. Diese optische Kontrolle kann automatisch erfolgen. Hierfür verwendet man so genannte AOI-Systeme (Automatic Optical Inspection). Die Leiterplattenoberfläche wird mittels einer Kamera aufgenommen und mit den zuvor aus den Layoutdaten erzeugten Daten verglichen. Fehlstellen zeigt der Computer an, so dass die Innenlagen entweder verworfen oder repariert werden können.

Hersteller von AOI Systemen für die Prüfung von Leiterplatten:

Orbotech Ltd. - www.orbotech.com

Sind die Innenlagen fertig hergestellt und fehlerfrei geprüft worden erfolgt die Vorbereitung zum Verpressen der Multilayer. Dafür muss die Oberfläche aktiviert werden, um eine gute Haftung zum Verbundwerkstoff zu gewährleisten.

Die aktivierten Innenlagen werden nun gemäß der im Arbeitsplan vermerkten Reihenfolge und Aufbauart abwechselnd mit dazwischen liegenden Prepregs übereinander gestapelt. Ein spezielles Aufnahmesystem sorgt für die nötigen Passungen der Lagen untereinander. Bei Prepregs handelt es sich um dünne Epoxydharzlagen im B-Zustand, die unter Hitze schmelzen und einen Verbund herstellen. Die Außenlagen können als einseitig kupferbeschichtete Lagen oder als reine Kupferfolie aufgetragen werden. Dieses flexible Aufbausystem ermöglicht unterschiedlichste Dicken oder auch asymmetrische Multilayer Leiterplatten. Die Multilayerpresse erhitzt die aufgebauten Pakete auf ca. 170° C und presst mit einem Druck von ca. 20 bar. Nach dem Verpressen der Multilayers gleicht die Leiterplatte einer herkömmlichen 2-lagigen kupferbeschichteten Platine. Die Innenlagen sind nicht erkennbar, es sind keine Löcher gebohrt. Lediglich die Kanten aus denen Epoxydharz ausgetreten sein kann weisen darauf hin, dass es sich um einen Multilayer handelt.

Anbieter von Multilayerpressen:

HML Multilayer GmbH - www.hml-hr.com

Bei Multilayern liegen im gebohrten Loch die Kupferschichten frei. Allerdings sind die Flächen durch die beim Bohren entstehende Wärme vom Harz verunreinigt, was die Durchkontaktierung verhindern kann. Diese Rückstände werden durch Oxydation mit mit Schwefelsäure, Chromsäure, Permanganat oder Sauerstoffplasma entfernt. Außerdem wird hierbei auch die Glasfaser etwas zurückgeätzt, um die Kupferfläche zu vergrößern.

Sind mehr als eine Kupferlage vorhanden, müssen die Lagen der Leiterplatten elektrisch miteinander verbunden werden. Dies erfolgt im Durchkontaktierungsprozess. Es gibt hier verschiedene Verfahren, die alle den Aufbau einer leitenden Verbindung in dem Loch zum Ziel haben. Am gebräuchlichsten sind:

Chemisch Kupfer

Hier wird in Bädern oder im Horizontalverfahren eine organische Palladiumschicht auf die Platte aufgebracht. Anschließend wird diese zu anorganischen Palladium "reduziert". Nun wird in einem Bad in dem Kupfer gelöst ist durch chemische Abscheidung Kupfer auf die gesamte Platte abgeschieden. Im allgemeinen etwa 4-6µ.

Black Hole

Hier wird die Platte im Horizontalverfahren mit einer Graphitlösung benetzt. Diese wird dann aufgetrocknet. Anschließend wird die Kohleschicht wieder vom Kupfer gestrippt. In den Löchern, wo die "raue" Glasfaser- und Epoxioberfläche ist haftet sie weiter an, und bildet so eine elektrisch leitende Oberfläche aus

Informationen und Anbieter für Leiterplattengalvanotechnik:

- Atotech Deutschland GmbH - www.atotech.com

- MacDermid Enthone - https://www.macdermidenthone.com/

- Höllmüller Maschinenbau GmbH - https://www.hms-germany.de/

Die Kupferdicke des Basismaterials bei mehrlagigen Leiterplatten ist geringer als die gewünschte Enddicke. Das hat den Vorteil dass nicht soviel Kupfer abgeätzt werden muss. Hierdurch können die Strukturen feiner werden und es wird Kupfer gespart. Um nun die gewünschte Dicke zu erreichen, wird mit galvanischer Abscheidung nun auf den freigelegten Leiterbahnen und in den Löchern Kupfer aufgebracht

Besuchen Sie unsere umfangreiche FAQ oder kontaktieren Sie uns mit Ihrem Anliegen. Gerne helfen wir Ihnen weiter.

Jeden dieser Prozesse in der Leiterplattenherstellung kann man in diverse Einzelschritte aufteilen. Die industrielle Leierplattenherstellung einer einfachen 2-lagigen Platine kommt somit auf ca. 100 Einzelschritte.

Wenn Sie möchten, können Sie sich das Flußdiagramm sowie den dazugehörigen Ablauf im praktischen .pdf Format downloaden.

| Name | Typ | Größe | Download |

|---|---|---|---|

| Leiterplattenherstellung Flussdiagramm mit Beschreibung(1073,06 KB, PDF) | 1073 KB | Download Anzeigen |

seit dem Jahr 2021

- CO2-neutral durch Kompensation

- Leiterplatten - außen grün, innen auch

- Expertise durch aktiven Austausch

- Expertise durch Schulung und Weiterbildung

- ISO 9001:2015 Qualitätsmanagement

- ISO 14001:2015 Umweltmanagement

- UL für starre FR4-Leiterplatten

- UL für flexible Leiterplatten

- UL für ALU IMS Leiterplatten